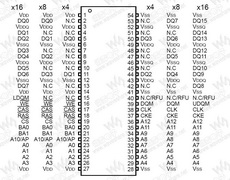

K4S561632E

技术资料——

K4S561632E PDF技术资料

K4S561632E 概述K4S561632E是一款268,435,456 bits高速SDRAM。K4S561632E采用三星电子的高性能CMOS工艺制造,其组织结构为4x4,194,304字,16bits位宽。K4S561632E的同步设计,再配合系统时钟I/O事务,使得每个时钟周期里的精细周期控制成为可能。工作频率范围、可编程突发长度、加上可编程潜伏期,这些特性让同样的K4S561632E器件得以适应许多的要求高带宽、高性能的存储系统应用。 |

|

|||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

K4S561632E 特性

|

||||||||||||||||||||||||||||||||||||||