USB Blaster用户手册

来自Waveshare Wiki

产品相关介绍

产品简介

USB Blaster适用于ALTERA CPLD/FPGA器件,可以通过计算机的USB接口对器件及其配置芯片进行编程、调试等操作。

USB Blaster功能简述

- 支持ALTERA 公司全系列CPLD/FPGA器件 - 支持ALTERA公司全系列主动串行配置器件 - 支持ALTERA公司全系列增强配置器件 - 支持AS﹑PS﹑JTAG三种下载模式 - 高速、稳定,内部采用FT245R+CPLD设计 - 支持1.2-5V编程电压 - 支持 SignalTap II 嵌入式逻辑分析仪 - 支持Nios II嵌入式处理器的通信和调试

支持的软件

- Quartus II集成开发环境 - NIOS II IDE 集成开发环境 - NIOS II EDS集成开发环境

支持的器件

- CPLD:MAX3000、MAX7000A/B/S、MAX9000和MAX II 等 - FPGA:Stratix、Stratix II、Cyclone、Cyclone II、CycloneIII、ACEX 1K、APEX 20K 和FLEX 10K等 - 主动串行配置器件:EPCS1、EPCS4、EPCS16等 - 增强配置器件:EPC1、EPC4 等 - 新器件不断增加中......

产品特性

- 采用高速下载方案:FT245+CPLD+244,下载速度接近原装ALTERA USB BLASTER - 相比其它下载方案,如68013或C8051F等方案,速度快1-3倍

与PC机的连接

- 通过USB 2.0接口与计算机连接

与目标板的连接

- 通过JTAG、AS或PS接口与目标板连接

USB Blaster状态灯说明

- 红灯是电源灯 - 绿灯是信号指示灯。进行软件下载时,绿灯闪烁说明下载正常

Altera USB Blaster用户手册(英文)

设备连接

设备连接与软硬件平台

一个完整的CPLD/FPGA开发环境,需具备“软件开发平台”和“硬件开发平台”。

软件开发平台:

- HDL开发软件:Quartus II - SOPC构建平台:SOPC Builder - DSP构建平台:DSP Builder - NIOS II软件开发平台:NIOS II EDS - 仿真软件:Modelsim-Altera - 另外对第三方综合、仿真等工具提供了软件接口

硬件开发平台:

硬件开发平台很简单,只需要一台PC、一条编程电缆便可对CPLD/FPGA进行在线配置或对配置芯片进行编程

连接到PC机

使用USB连接PC机

第一次把设备连接至电脑,您需要安装设备驱动,驱动由ALTERA公司提供,随Quartus II 软件一起提供给用户。 安装过程详见:![]() USB Blaster驱动安装教程

USB Blaster驱动安装教程

图示安装教程:

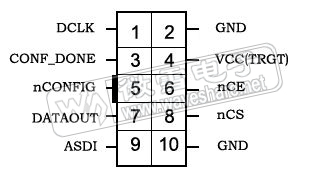

连接到目标板的接口简介

下表为JTAG、AS、PS接口定义:

| JTAG | AS | PS | ||||

| PIN | 信号 | 描述 | 信号 | 描述 | 信号 | 描述 |

1

|

TCK | 时钟信号 | DCLK | 时钟信号 | DCLK | 时钟信号 |

2

|

GND | 信号地 | GND | 信号地 | GND | 信号地 |

3

|

TDO | 数据输出 | CONF_DONE | 配置完成 | CONF_DONE | 配置完成 |

4

|

VCC(TRGT) | 电源 | VCC(TRGT) | 电源 | VCC(TRGT) | 电源 |

5

|

TMS | JTAG状态机控制 | nCONFIG | 配置控制 | nCONFIG | 配置控制 |

6

|

NC | nCE | cyclone芯片使能 | NC | ||

7

|

NC | DATAOUT | 主动串行数据输出 | nSTATUS | 配置状态 | |

8

|

NC | nCS | 串行设备选择 | NC | ||

9

|

TDI | 数据输入 | ASDI | 主动串行数据输入 | DATA0 | 数据输入 |

10

|

GND | 信号地 | GND | 信号地 | GND | 信号地 |

软件使用说明

软件简介

FPGA常用开发软件简介

| 软件名称 | 简介 |

|---|---|

| Quartus II | Quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。 |

| SOPC Builder | SOPC Builder是一个强大的系统开发工具,能使用户在很短的时间内定义并且生成一个片上系统;SOPC Builder作为Quartus II 软件的一部分提供给用户。 |

| NIOS II EDS | NIOS II EDS(NIOS II Embeded Development Suite)是一款面对所有NIOS II处理器的软件开发环境。只需要一个运行在PC上的NIOS II EDS软件,一个ALTERA FPGA,一条下载电缆,用户就能进行NIOS II系统的程序编写或者与SOPC系统通信。 |

| SignalTap II | SignalTap II全称SignalTap II Logic Analyzer,是一款功能强大且极具实用性的FPGA片上debug工具软件,可以捕获和显示实时信号,观察在系统设计中的硬件和软件之间的互相作用。 |

| Modelsim-Altera | Mentor公司为ALTERA CPLD/FPGA量身定做的一款仿真软件,具有RTL级和门级仿真等功能。 |

通过开发板的JTAG接口既能实现对FPGA器件的在线配置,也可编程串行配置器件。

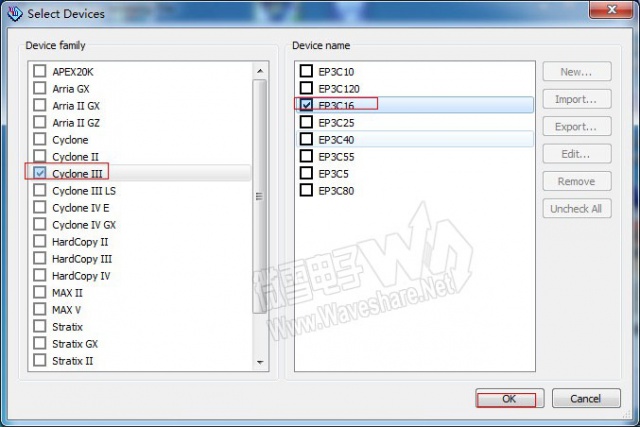

| 以下配置皆以EP3C16为例,配置时要选对应的芯片型号,如:你用的芯片是Cyclone II系列的EP2C8,那么下面操作涉及到配置为Cyclone III的改为Cyclone II,涉及到配置为EP3C16的改为EP2C8 |

利用JTAG接口在线配置FPGA(掉电后配置丢失,需要重新下载)

使用Quartus II下载示例程序中的Verilog和VHDL,可参看视频教程:

在您编译完成后,就可进行配置信息的下载了,图示具体步骤如下:

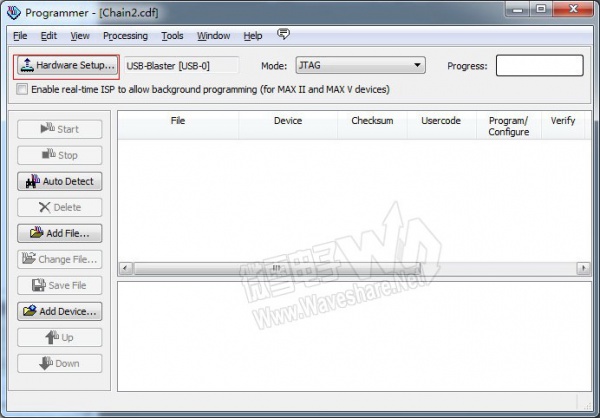

- Tools-> Programmer,打开Programmer对话框,如下图所示:

- 点击左上角Hardware setup,如下图所示:

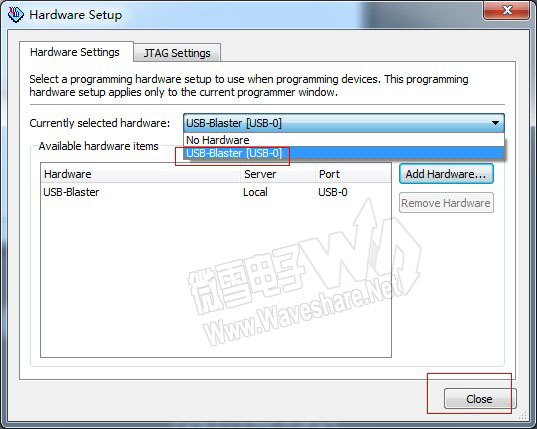

- 打开Currently selected hardware下拉菜单,选择USB_blaster,然后单击close,如下图所示:

- 点击Add file,选择Quartus ii 生成的SOF文件,之后勾选program/configure,如下图:

- 点击Start,配置开始。

利用JTAG接口编程串行配置器件(掉电后配置不丢失)

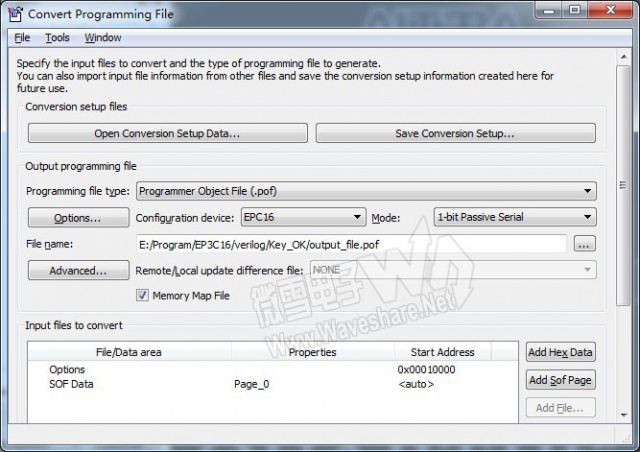

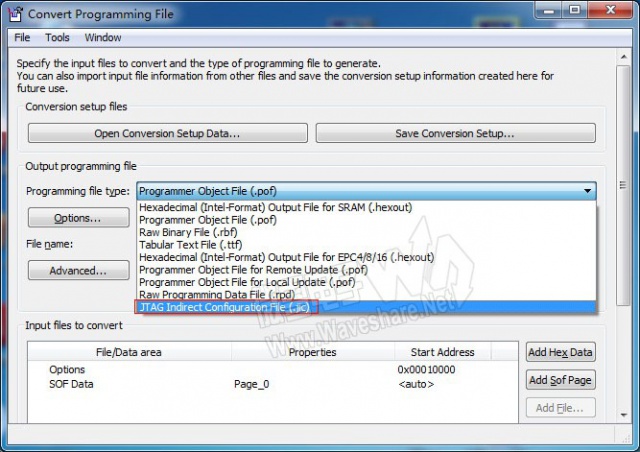

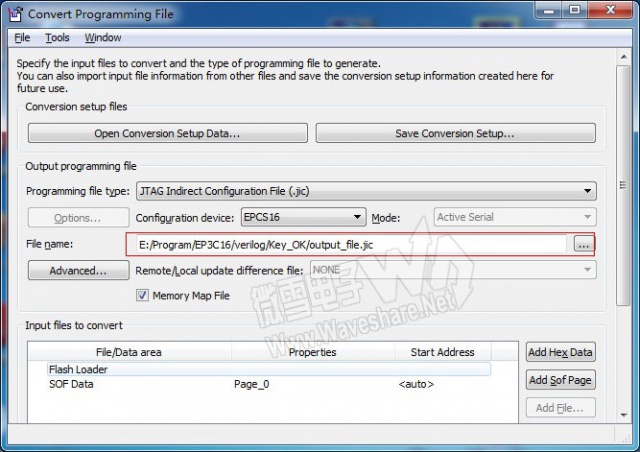

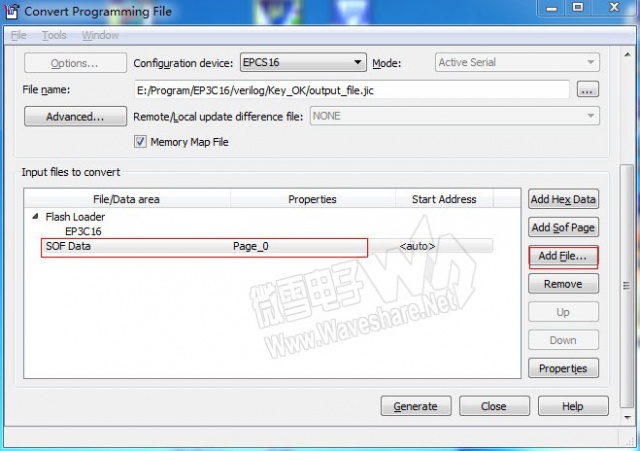

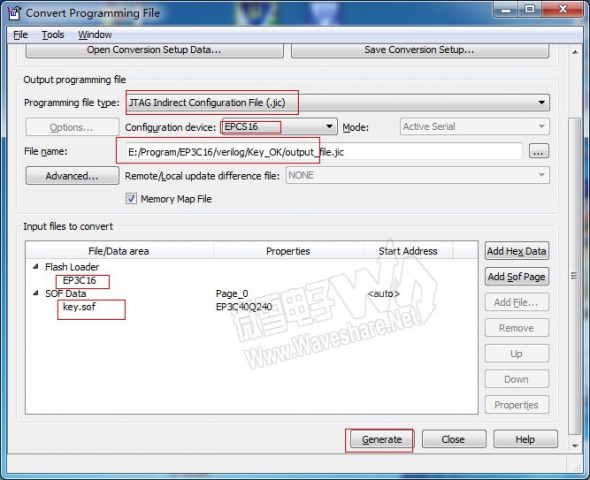

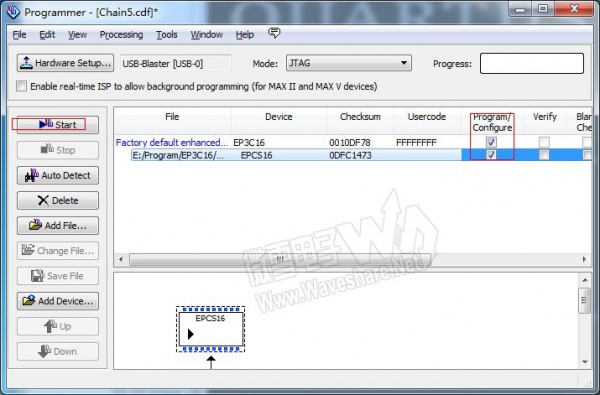

- 在File菜单下拉菜单中选择convert/programming files,操作步骤如下图: