模板: Altera-Hardware-Design-Basic-II

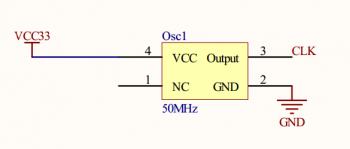

时钟电路

在FPGA设计中时钟的最好解决方案是:由专用的全局时钟输入引脚驱动的单个主时钟去钟控设计中的每一个时序器件,只要有可能就因该尽量在设计项目中采用全局时钟,FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。在器件中,这种全局时钟能提供最短的是在延时。在设计中我们用到一个全局时钟口CLK,由于它是单个时钟口,所有我们考虑用有源晶振时钟作为外部时钟来源。板字采用的是50MHz的晶振,为系统提供精准的时钟源,其原理图如下:

| 引脚名称 | 描述 |

|---|---|

| CLK | 时钟输入 |

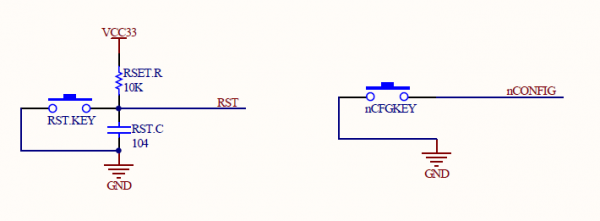

复位电路

复位电脑包括RST复位电路和nCONFIG重置电路。RST复位采用RESET按键开关构成的阻容复位电路,按下后,低电平有效产生复位信号。nCONFIG重置电路则由nCONFIG按键来触发,按下后可以使FPGA进行重新配置而不需要重启板子电源。其原理图如下:

| 引脚名称 | 描述 |

|---|---|

| RESET | 低电平复位 |

| nCONFIG | 低电平复位,恢复逻辑高电平即重新配置 |

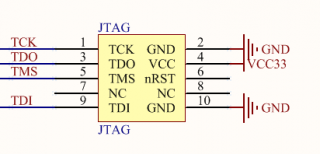

配置/下载接口

配置又称加载或下载,是对FPGA内容进行编程的一个过程。每次上电后需要进行配置是基于SRAM工艺FPGA的一个特点。在FPGA内部,有许多可编程的多路器、逻辑、互连线节点和RAM初始化内容等,都需要配置数据来控制。FPGA中配置RAM就起到了这样一个作用,它存放了配置数据的内容。

根据FPAG在配置电路中的角色,其配置数据可以使用3种方式载入(Download)到目标器件,这三种分别是:FPGA主动(Active)方式、FPGA被动(Passive)方法和JTAG方式。JTAG接口是一个业界标准接口,Altera FPGA基本上都可以支持JTAG命令来配置FPGA,而且JTAG配置方式比其他任何一种配置方式优先级都高,因此,我们在板子提供了JTAG配置方式,其配置接口电路图如下所示:

用户可以使用专用的Altera下载器USB Blaster[1]进行下载调试。如需编程到EPCS芯片需要对下载文件格式进行转换[2]

| 引脚名称 | 描述 |

|---|---|

| TDI | 用于测试数据的输入 |

| TDO | 用于测试数据的输出 |

| TMS | 模式控制管脚,决定JTAG电路内部的TAP状态机的跳转 |

| TCK | 测试时钟,其他信号线都必须与之同步 |

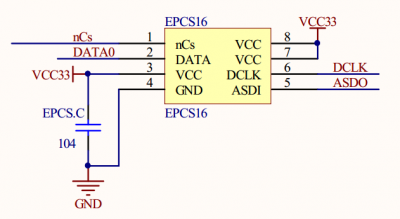

配置电路

为了使FPGA掉电后仍然能够保持程序数据,FPGA需要外接配置芯片,这里选用了Altera公司的串行FLASH存储器EPCS16。EPCS16属于增强型配置器件,容量高达16Mbit,支持对打容量FPGA的单片配置,它们可以由JTAG接口进行在系统编程(In System Programming)。其对应配置电路原理图如下:

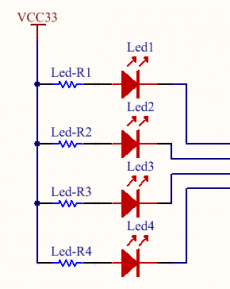

LED电路

板载4个用户LED,每个LED都是直接由FPGA芯片上一个引脚来驱动的,当给对应的引脚一个逻辑低电平时,点亮LED,原理图如下所示:

扩展板接口

这一系列Open板子采用核心板和扩展板分离的方式,这种灵活的设计模式一方面方便用户根据自己的需求自行设计外接电路,方便快捷;另一方面核心板和底板接口设计充分考虑了与其他FPGA板子的兼容和通用性,方便用户升级换代。

- ↑ USB Blaster产品简介

- ↑ 通过JTAG口对FPGA器件进行在线配置(也称可编程串行配置),详见:USB Blaster