ATmega48 时钟源

以下资料参考马潮老师的中文手册,由微雪电子整理并发布,转载请注明出处:www.waveshare.net,否则追究相应责任!

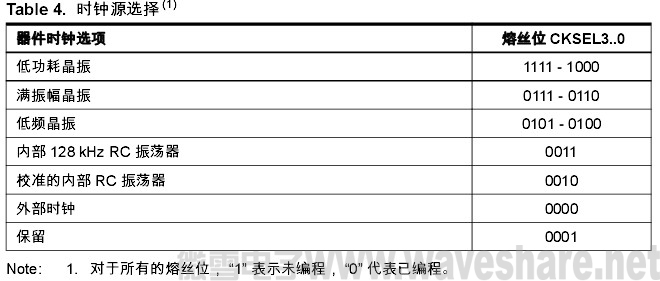

ATmega48芯片有如下几种通过Flash熔丝位进行选择的时钟源。时钟输入到AVR时钟发生器,再分配到相应的模块。

不同的时钟选项将在后续部分进行介绍。任何时钟源都需要足够高的Vcc来启动振荡器,并且还要有一个最小振荡周期以保证在开

始正常工作之前电源达到稳定电平 。

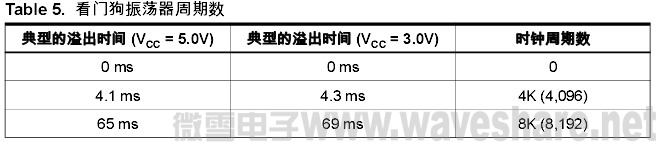

延时的主要目的是保证在系统能够提供符合应用要求的最小的Vcc之前 AVR处于复位状态。延时过程之中 MCU 并不监控实际的电压。因此需要用户选择合适的、长于 Vcc 上升时间的延时时间。如果无法做到这一点,就应该使用内 / 外部 BOD。 BOD 电路可以保证在释放复位之前有足够高的 Vcc。使用 BOD 时可以禁止超时延迟。我们不推荐在没有使用 BOD 电路时禁止超时延迟的设计。 缺省时钟源 ATmega48/88/168器件出厂时内部 RC 振荡器频率标定为 8.0MHz 并且 CKDIV8 被编程,得到 1.0MHz 的系统时钟。启动时间设为最长且定时周期使能。(CKSEL = "0010", SUT = "10",CKDIV8= "0")。这种设置保证用户可以通过任何有效的编程接口获得需要的时钟源。 |

|---|

| 相关AVR资料说明 |

可作为如下AVR的参考资料: ATtiny13 ATtiny24 ATtiny44 ATtiny84 ATtiny2313 ATtiny26 ATmega48 ATmega88 ATmega168 ATmega8 ATmega16 ATmega32 ATmega64 ATmega128 ATmega162 ATmega169 ATmega169P ATmega8515 ATmega8535

| 相关AVR型号资料 |

| ATtiny13 | ATtiny24 | ATtiny44 | ATtiny84 | ATtiny26 | ATtiny2313 |

| ATmega48 | ATmega88 | ATmega168 | ATmega8 | ATmega16 | ATmega32 |

| ATmega64 | ATmega128 | ATmega162 | ATmega169 | ATmega8515 | ATmega8535 |

ATmega48 时钟源

——