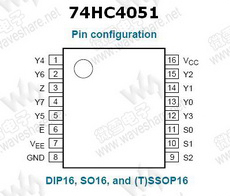

74HC4051

技术资料——

74HC4051 PDF技术资料

74HC4051 概述74HC4051是一款高速CMOS器件,74HC4051引脚兼容低功耗肖特基TTL(LSTTL)系列。74HC4051遵循JEDEC标准no.7A。 74HC4051是8通道模拟多路选择器/多路分配器,带有3个数字选择端(S0至S2),1个低有效使能端(E),8个独立输入/输出端(Y0至Y7)和1个公共输入/输出端(Z)。 E为低时,8个开关的其中之一将被S0至S2选中(低阻态)。E为高时,所有开关都进入高阻态,直接无视S0至S2。 VCC和GND是数字控制端(S0至S2,E)的供电引脚,74HC4051的VCC至GND范围为2.0 V~10.0 V。74HC4051的模拟输入/输出端(Y0至Y7,Z)在上限VCC和下限VEE之间摆动,VCC-VEE应当不超过10.0 V。 作为一个数字多路选择器/多路分配器,VEE将被连接到GND上(一般是接地)。 |

|

|||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

74HC4051 特性

|

||||||||||||||||||||||||||||||||